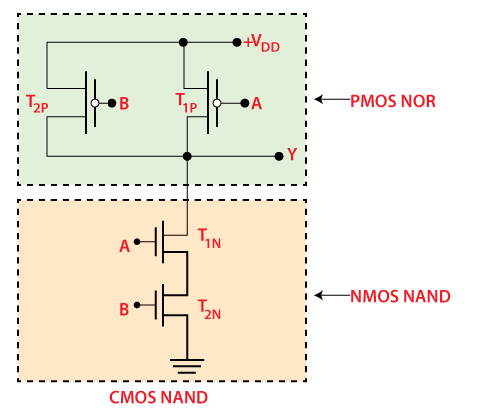

Both are used in several digital logic circuits and functions, static RAM, and microprocessors. Thus, if both transistors have their gates connected to a similar input, the p-type MOSFET will be ON when the n-type MOSFET is OFF, and vice-versa.ĬMOS and NMOS both moved by the expansion in digital technologies, that are used to build the integrated circuits.

In its place of the load resistor of NMOS logic gates, CMOS has a set of P-type MOSFETs in a pull-up n/w between the high voltage rail and the o/p. In CMOS logic gates, a collection of n-type MOSFETs is located in a pull-down network between the low voltage power supply rail and the o/p. The output after crossing through one, the NMOS gate would be VDD-Vt. CMOS transmits both logic 0 logic 1 and NMOS only logic 1 i.e, VDD. CMOS and NMOS are two logic families, where CMOS uses both MOS transistors and PMOS for design and NMOS use only field-effect transistors for design.ĬMOS is selected over NMOS for the designing of an embedded system. NMOS-Inverter Why CMOS Technology is Preferred Over NMOS TechnologyĬMOS stands for Complementary Metal-Oxide-Semiconductor whereas NMOS is a negative channel metal oxide semiconductor. Indifference, Positive channel MOS -PMOS works by moving electron positions. So that transistors are switched by the movement of the electron. It is a kind of semiconductor that charges negatively. The acronym of NMOS is a negative channel metal oxide semiconductor it is pronounced as en-moss. If we mold each transistor as an easy switch triggered by the input voltage, the inverter’s actions can be seen very simply. It is significant to observe that the CMOS doesn’t have any resistors, which creates more power capacity than a regular resistor MOSFET inverter.Īs the voltage at the CMOS device input changes between 0 & 5 volts, the condition of the NMOS and PMOS changes accordingly. MOSFET states at different input voltages, and power failures due to electrical current.Ī CMOS inverter has two transistors namely a PMOS transistor and an NMOS transistor that is connected to the gate and drain terminals, a VDD (voltage supply) at the PMOS source terminal, and a GND terminal connected to the NMOS source terminal, where the input voltage is connected to the gate terminals and output terminal is connected to the drain terminals. The small explanation of the inverters gives a basic understanding of the operation of the inverter. Also, this inverter has good logic buffer characteristics. These inverters can function at high-speed and with less power loss. The high density of logic functions on a chipįor any IC technology, the logic inverter plays a vital role in the designing of a digital circuit, Once the process of an inverter circuit is cautiously understood, the consequences can be extended to the logic gates design and complex circuits.ĬMOS inverters are MOSFET inverters, which are most widely used in chip design.The benefits of CMOS technology over NMOS technology include the following. Advantages of CMOS TechnologyĬMOS technology devices are used in a variety of applications with analog circuits such as data converters, image sensors, etc. Due to this cause, CMOS technology is most widely used and is executed in VLSI chips. This permits a high density of logic tasks on a chip. For instance, TTL or MOS logic have normally some standing current even when not the varying state. So, MOS devices do not generate as much dissipate heat as other types of logic.

#Cmos transistor diagram series#

When the pair of transistors is in OFF condition, the grouping of series draws important power only throughout switching between ON & OFF states. The CMOS and NMOS technology differences can be simply distinguished with their working principles, advantages, and disadvantages as discussed. BiCMOS technology has finished it possible to unite bipolar devices and CMOS transistors in a single process at a sensible cost to get the high-density integration of MOS logic CMOS and NMOS technology Difference CMOS technology gives high input and low output impedance, symmetrical noise margins, high packing density, and low power dissipation. Since they use less power, and metal oxide semiconductor permits higher integration.īiCMOS Technology can be built with the CMOS and Bipolar transistors these are incorporated on a similar semiconductor chip. When the voltage is applied to the gate terminal, then it controls the flow of current between the terminals of the source and drain. At present, Polysilicon is generally used as a gate terminal. These technologies comprise a semiconductor, a metal gate, and oxide. Metal oxide semiconductor (MOS) is further divided into different technologies beneath NMOS, PMOS, and CMOS.

0 kommentar(er)

0 kommentar(er)